FPGA Learning Series: 7. Serial-to-parallel conversion

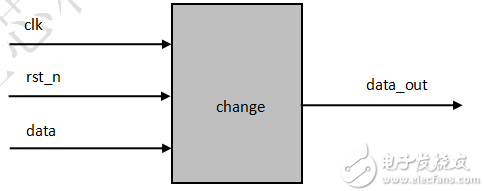

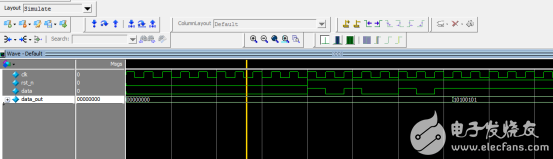

design background: Verilog grammar has used the idea of ​​serial-to-parallel conversion in many cases. It aims to increase the speed of operation and chip operation. Serial-to-parallel has become an indispensable thinking in design.  Design principle :  This design master designed an 8-bit serial-to-parallel conversion, meaning that when 8 data were input, we converted the 8 serial data into 8-bit parallel data and then output it. That is, an 8-bit register is needed to save a data bit to the corresponding bit, and then output to complete the design.  Design architecture diagram : Design code : Design module 0  Module study ( clk , rst_n , data , data_out );  // Port list 1  2  Input clk , rst_n ;             // clock, reset input 3  Input data ;                   // input data 4  5  Output  Reg  [ 7 : 0 ] data_out ; 6  7  Reg  [ 3 : 0 ] count ;  8  Reg  [ 7 : 0 ] temp ; 9  10 always  @  ( posedge clk )      // sequential logic 11 if (! rst_n ) 12 begin 13 data_out <=  0 ; 14 temp <=  0 ; 15 count <=  0 ; 16 end 17 else  If ( count <  8 )         // counts only 8 data 18 begin 19 temp <=  { temp [ 6 : 0 ], data };   // shift register 20 count <= count + 1'b1 ; 21 end 22 else 23 begin 24 data_out <= temp ;    // After receiving the output 25 end 26 27  Endmodule  Test module 0  `timescale  1ns  /  1ps  // Time scale 1  2  Module tb (); 3  4  Reg clk , rst_n ; 5  Reg data ; 6  7  Wire  [ 7 : 0 ] data_out ; 8  9  Study study_dut (        // Design example 10 . clk ( clk ),  11 . rst_n ( rst_n ), 12. Data (data), 13. Data_out (data_out) 14 ); 15 16 initial   Begin 17 clk =  1 ;   18 rst_n =  0 ;   // reset 19 data =  0 ; 20 # 200 rst_n =  1 ;       // Do not reset 21 data =  1 ;         // Analog data input 22 # 20 data =  0 ; 23 # 20 data =  1 ; 24 # 20 data =  0 ; 25 26 # 20 data =  0 ; 27 # 20 data =  1 ; 28 # 20 data =  0 ; 29 # 20 data =  1 ; 30 31 # 200  $stop ; 32 end 33 34 always  # 10 clk =~ clk ;     // Analog crystal clock 35 36  Endmodule   Simulation diagram : In the test, the analog data input is 1010 0101, and the output is a parallel data. Then, by looking at the simulation timing, it is clear that the output is 8-bit parallel data. This design is correct. Also, we can infer and design logic circuits of our own. A manual pulse generator (MPG) is a device normally associated with computer numerically controlled machinery or other devices involved in positioning. It usually consists of a rotating knob that generates electrical pulses that are sent to an equipment controller. The controller will then move the piece of equipment a predetermined distance for each pulse. Manual Pulse Generator,Handwheel MPG CNC,Electric Pulse Generator,Signal Pulse Generator Jilin Lander Intelligent Technology Co., Ltd , https://www.jilinlandermotor.com

Â

Â

The CNC handheld controller MPG Pendant with x1, x10, x100 selectable. It is equipped with our popular machined MPG unit, 4,5,6 axis and scale selector, emergency stop and reset button.