DMA controller design for real-time image processing system

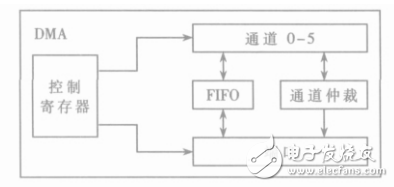

Abstract: Based on the analysis of the structure of traditional DMA controller, aiming at the data transmission requirements of real-time image processing system, an optimization method such as multi-port module design, adding RoundRobin channel priority arbitration algorithm and optimizing data transmission channel is proposed to improve the data. Transmission speed and improved address generation mode to meet the requirements of image algorithms. Digital image processing is one of the most widely used applications in embedded systems. At present, digital image processing technology is increasingly used in scientific research, industrial production or management. Target tracking, robot navigation, autopilot, traffic monitoring and other applications have also greatly promoted the development of real-time image processing technology. Digital image processing is characterized by large amount of data, complicated operation, and strong real-time performance. Generally, the amount of data is often larger than the on-chip storage capacity. For a processing system with limited on-chip storage resources, it is generally necessary to borrow external storage space. In order to improve the real-time processing capability of the system, direct memory (DMA) must be used for data exchange between the on-chip high-speed memory area and the external memory space, so that the processor only focuses on data calculation. The DMA controller generally has the following functions: fast data transmission between different storage media; high-speed data exchange independent of the processor; multiple DMA channels to improve parallelism of data transmission; support data burst transmission mode; Priority programmable arbitration mechanism. Figure 1 is a block diagram of the DMA controller. As can be seen from the figure, the DMA controller is mainly composed of the following modules: Figure 1 DMA controller module diagram (1) Register Control Module: Provides a programmable interface for the software programmer to control the working state of the DMA; controls the working state of each DMA channel and each port according to different settings of each configuration bit. (2) Channel control module: There are 6 DMA channels that can work independently in the DMA controller. The DMA application is submitted according to the configuration bits of the corresponding control register, and the storage medium is accessed through the port module. (3) Port Control Module: It is an interface module between the DMA controller and the storage medium, providing access to the address, data and control signal lines of the storage medium. (4) FIFO control module: There are six 32-byte buffer queues in the DMA controller, which are occupied by each channel. In the bursty transmission, the data in the slow storage device can be cached, thereby improving the DMA control. The transmission speed of the device. (5) Channel priority arbitration module: When multiple DMA channels simultaneously submit DMA applications, priority arbitration of the channel is required, and hardware priority arbitration is used here. In addition, there are interrupt and event response modules to ensure real-time transmission of DMA. First, in the traditional DMA design, the port module uses only one set of data lines, address lines, and control lines to connect all the storage media that the DMA needs to connect; and when multiple channels need to occupy the data lines, address lines, and control lines at the same time. It is handled only by hardware priority arbitration. Thus, for real-time image processing systems of a large number of DMA applications, the transmission efficiency of DMA is not high, which affects the image processing effect of the entire system. Therefore, some improvements need to be made to the DMA port module and the priority arbitration module in order to effectively improve the data transfer rate of the DMA. Moreover, the data transfer path of the DMA can also be improved. Secondly, some format characteristics of the image data itself and the required image processing algorithms determine that data transmission in a real-time image processing system is not a simple data transmission, but requires that DMA data transmission has both matrix transmission and flip transmission. And other functions to speed up image processing and meet the requirements of some image processing algorithms. The ordinary DMA address generation module does not have such a design. Chetak Gensets,Diesel Generator,Portable Generator Silent,High Output Dc Generator Wuxi Doton Power , https://www.dotonpower.com